mirror of

https://github.com/esp8266/Arduino.git

synced 2025-11-30 05:24:00 +03:00

Merge remote-tracking branch 'esp8266/master'

This commit is contained in:

@@ -814,6 +814,7 @@ wifinfo.build.f_cpu=80000000L

|

|||||||

wifinfo.build.core=esp8266

|

wifinfo.build.core=esp8266

|

||||||

wifinfo.build.variant=wifinfo

|

wifinfo.build.variant=wifinfo

|

||||||

wifinfo.build.flash_mode=qio

|

wifinfo.build.flash_mode=qio

|

||||||

|

wifinfo.build.board=ESP8266_ESP12

|

||||||

wifinfo.build.spiffs_pagesize=256

|

wifinfo.build.spiffs_pagesize=256

|

||||||

|

|

||||||

#wifinfo.menu.ESPModule.ESP07512=ESP07 (1M/512K SPIFFS)

|

#wifinfo.menu.ESPModule.ESP07512=ESP07 (1M/512K SPIFFS)

|

||||||

|

|||||||

@@ -177,26 +177,7 @@ uint32_t EspClass::getFlashChipSize(void)

|

|||||||

uint8_t * bytes = (uint8_t *) &data;

|

uint8_t * bytes = (uint8_t *) &data;

|

||||||

// read first 4 byte (magic byte + flash config)

|

// read first 4 byte (magic byte + flash config)

|

||||||

if(spi_flash_read(0x0000, &data, 4) == SPI_FLASH_RESULT_OK) {

|

if(spi_flash_read(0x0000, &data, 4) == SPI_FLASH_RESULT_OK) {

|

||||||

switch((bytes[3] & 0xf0) >> 4) {

|

return magicFlashChipSize((bytes[3] & 0xf0) >> 4);

|

||||||

case 0x0: // 4 Mbit (512KB)

|

|

||||||

return (512_kB);

|

|

||||||

case 0x1: // 2 MBit (256KB)

|

|

||||||

return (256_kB);

|

|

||||||

case 0x2: // 8 MBit (1MB)

|

|

||||||

return (1_MB);

|

|

||||||

case 0x3: // 16 MBit (2MB)

|

|

||||||

return (2_MB);

|

|

||||||

case 0x4: // 32 MBit (4MB)

|

|

||||||

return (4_MB);

|

|

||||||

case 0x5: // 64 MBit (8MB)

|

|

||||||

return (8_MB);

|

|

||||||

case 0x6: // 128 MBit (16MB)

|

|

||||||

return (16_MB);

|

|

||||||

case 0x7: // 256 MBit (32MB)

|

|

||||||

return (32_MB);

|

|

||||||

default: // fail?

|

|

||||||

return 0;

|

|

||||||

}

|

|

||||||

}

|

}

|

||||||

return 0;

|

return 0;

|

||||||

}

|

}

|

||||||

@@ -207,18 +188,7 @@ uint32_t EspClass::getFlashChipSpeed(void)

|

|||||||

uint8_t * bytes = (uint8_t *) &data;

|

uint8_t * bytes = (uint8_t *) &data;

|

||||||

// read first 4 byte (magic byte + flash config)

|

// read first 4 byte (magic byte + flash config)

|

||||||

if(spi_flash_read(0x0000, &data, 4) == SPI_FLASH_RESULT_OK) {

|

if(spi_flash_read(0x0000, &data, 4) == SPI_FLASH_RESULT_OK) {

|

||||||

switch(bytes[3] & 0x0F) {

|

return magicFlashChipSpeed(bytes[3] & 0x0F);

|

||||||

case 0x0: // 40 MHz

|

|

||||||

return (40_MHz);

|

|

||||||

case 0x1: // 26 MHz

|

|

||||||

return (26_MHz);

|

|

||||||

case 0x2: // 20 MHz

|

|

||||||

return (20_MHz);

|

|

||||||

case 0xf: // 80 MHz

|

|

||||||

return (80_MHz);

|

|

||||||

default: // fail?

|

|

||||||

return 0;

|

|

||||||

}

|

|

||||||

}

|

}

|

||||||

return 0;

|

return 0;

|

||||||

}

|

}

|

||||||

@@ -230,10 +200,53 @@ FlashMode_t EspClass::getFlashChipMode(void)

|

|||||||

uint8_t * bytes = (uint8_t *) &data;

|

uint8_t * bytes = (uint8_t *) &data;

|

||||||

// read first 4 byte (magic byte + flash config)

|

// read first 4 byte (magic byte + flash config)

|

||||||

if(spi_flash_read(0x0000, &data, 4) == SPI_FLASH_RESULT_OK) {

|

if(spi_flash_read(0x0000, &data, 4) == SPI_FLASH_RESULT_OK) {

|

||||||

mode = (FlashMode_t) bytes[2];

|

mode = magicFlashChipMode(bytes[2]);

|

||||||

if(mode > FM_DOUT) {

|

}

|

||||||

mode = FM_UNKNOWN;

|

return mode;

|

||||||

}

|

}

|

||||||

|

|

||||||

|

uint32_t EspClass::magicFlashChipSize(uint8_t byte) {

|

||||||

|

switch(byte & 0x0F) {

|

||||||

|

case 0x0: // 4 Mbit (512KB)

|

||||||

|

return (512_kB);

|

||||||

|

case 0x1: // 2 MBit (256KB)

|

||||||

|

return (256_kB);

|

||||||

|

case 0x2: // 8 MBit (1MB)

|

||||||

|

return (1_MB);

|

||||||

|

case 0x3: // 16 MBit (2MB)

|

||||||

|

return (2_MB);

|

||||||

|

case 0x4: // 32 MBit (4MB)

|

||||||

|

return (4_MB);

|

||||||

|

case 0x5: // 64 MBit (8MB)

|

||||||

|

return (8_MB);

|

||||||

|

case 0x6: // 128 MBit (16MB)

|

||||||

|

return (16_MB);

|

||||||

|

case 0x7: // 256 MBit (32MB)

|

||||||

|

return (32_MB);

|

||||||

|

default: // fail?

|

||||||

|

return 0;

|

||||||

|

}

|

||||||

|

}

|

||||||

|

|

||||||

|

uint32_t EspClass::magicFlashChipSpeed(uint8_t byte) {

|

||||||

|

switch(byte & 0x0F) {

|

||||||

|

case 0x0: // 40 MHz

|

||||||

|

return (40_MHz);

|

||||||

|

case 0x1: // 26 MHz

|

||||||

|

return (26_MHz);

|

||||||

|

case 0x2: // 20 MHz

|

||||||

|

return (20_MHz);

|

||||||

|

case 0xf: // 80 MHz

|

||||||

|

return (80_MHz);

|

||||||

|

default: // fail?

|

||||||

|

return 0;

|

||||||

|

}

|

||||||

|

}

|

||||||

|

|

||||||

|

FlashMode_t EspClass::magicFlashChipMode(uint8_t byte) {

|

||||||

|

FlashMode_t mode = (FlashMode_t) byte;

|

||||||

|

if(mode > FM_DOUT) {

|

||||||

|

mode = FM_UNKNOWN;

|

||||||

}

|

}

|

||||||

return mode;

|

return mode;

|

||||||

}

|

}

|

||||||

@@ -298,6 +311,24 @@ uint32_t EspClass::getFlashChipSizeByChipId(void) {

|

|||||||

}

|

}

|

||||||

}

|

}

|

||||||

|

|

||||||

|

/**

|

||||||

|

* check the Flash settings from IDE against the Real flash size

|

||||||

|

* @param needsEquals (return only true it equals)

|

||||||

|

* @return ok or not

|

||||||

|

*/

|

||||||

|

bool EspClass::checkFlashConfig(bool needsEquals) {

|

||||||

|

if(needsEquals) {

|

||||||

|

if(getFlashChipRealSize() == getFlashChipSize()) {

|

||||||

|

return true;

|

||||||

|

}

|

||||||

|

} else {

|

||||||

|

if(getFlashChipRealSize() >= getFlashChipSize()) {

|

||||||

|

return true;

|

||||||

|

}

|

||||||

|

}

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

String EspClass::getResetInfo(void) {

|

String EspClass::getResetInfo(void) {

|

||||||

if(resetInfo.reason != 0) {

|

if(resetInfo.reason != 0) {

|

||||||

char buff[200];

|

char buff[200];

|

||||||

|

|||||||

@@ -117,6 +117,12 @@ class EspClass {

|

|||||||

FlashMode_t getFlashChipMode();

|

FlashMode_t getFlashChipMode();

|

||||||

uint32_t getFlashChipSizeByChipId();

|

uint32_t getFlashChipSizeByChipId();

|

||||||

|

|

||||||

|

uint32_t magicFlashChipSize(uint8_t byte);

|

||||||

|

uint32_t magicFlashChipSpeed(uint8_t byte);

|

||||||

|

FlashMode_t magicFlashChipMode(uint8_t byte);

|

||||||

|

|

||||||

|

bool checkFlashConfig(bool needsEquals = false);

|

||||||

|

|

||||||

bool flashEraseSector(uint32_t sector);

|

bool flashEraseSector(uint32_t sector);

|

||||||

bool flashWrite(uint32_t offset, uint32_t *data, size_t size);

|

bool flashWrite(uint32_t offset, uint32_t *data, size_t size);

|

||||||

bool flashRead(uint32_t offset, uint32_t *data, size_t size);

|

bool flashRead(uint32_t offset, uint32_t *data, size_t size);

|

||||||

|

|||||||

@@ -57,6 +57,14 @@ bool UpdaterClass::begin(size_t size, int command) {

|

|||||||

return false;

|

return false;

|

||||||

}

|

}

|

||||||

|

|

||||||

|

if(!ESP.checkFlashConfig(false)) {

|

||||||

|

_error = UPDATE_ERROR_FLASH_CONFIG;

|

||||||

|

#ifdef DEBUG_UPDATER

|

||||||

|

printError(DEBUG_UPDATER);

|

||||||

|

#endif

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

_reset();

|

_reset();

|

||||||

_error = 0;

|

_error = 0;

|

||||||

|

|

||||||

@@ -116,9 +124,13 @@ bool UpdaterClass::begin(size_t size, int command) {

|

|||||||

return true;

|

return true;

|

||||||

}

|

}

|

||||||

|

|

||||||

void UpdaterClass::setMD5(const char * expected_md5){

|

bool UpdaterClass::setMD5(const char * expected_md5){

|

||||||

if(strlen(expected_md5) != 32) return;

|

if(strlen(expected_md5) != 32)

|

||||||

|

{

|

||||||

|

return false;

|

||||||

|

}

|

||||||

_target_md5 = expected_md5;

|

_target_md5 = expected_md5;

|

||||||

|

return true;

|

||||||

}

|

}

|

||||||

|

|

||||||

bool UpdaterClass::end(bool evenIfRemaining){

|

bool UpdaterClass::end(bool evenIfRemaining){

|

||||||

@@ -152,6 +164,7 @@ bool UpdaterClass::end(bool evenIfRemaining){

|

|||||||

#ifdef DEBUG_UPDATER

|

#ifdef DEBUG_UPDATER

|

||||||

DEBUG_UPDATER.printf("MD5 Failed: expected:%s, calculated:%s\n", _target_md5.c_str(), _md5.toString().c_str());

|

DEBUG_UPDATER.printf("MD5 Failed: expected:%s, calculated:%s\n", _target_md5.c_str(), _md5.toString().c_str());

|

||||||

#endif

|

#endif

|

||||||

|

_reset();

|

||||||

return false;

|

return false;

|

||||||

}

|

}

|

||||||

#ifdef DEBUG_UPDATER

|

#ifdef DEBUG_UPDATER

|

||||||

@@ -159,6 +172,14 @@ bool UpdaterClass::end(bool evenIfRemaining){

|

|||||||

#endif

|

#endif

|

||||||

}

|

}

|

||||||

|

|

||||||

|

if(!_verifyEnd()) {

|

||||||

|

#ifdef DEBUG_UPDATER

|

||||||

|

printError(DEBUG_UPDATER);

|

||||||

|

#endif

|

||||||

|

_reset();

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

if (_command == U_FLASH) {

|

if (_command == U_FLASH) {

|

||||||

eboot_command ebcmd;

|

eboot_command ebcmd;

|

||||||

ebcmd.action = ACTION_COPY_RAW;

|

ebcmd.action = ACTION_COPY_RAW;

|

||||||

@@ -233,12 +254,70 @@ size_t UpdaterClass::write(uint8_t *data, size_t len) {

|

|||||||

return len;

|

return len;

|

||||||

}

|

}

|

||||||

|

|

||||||

|

bool UpdaterClass::_verifyHeader(uint8_t data) {

|

||||||

|

if(_command == U_FLASH) {

|

||||||

|

// check for valid first magic byte (is always 0xE9)

|

||||||

|

if(data != 0xE9) {

|

||||||

|

_error = UPDATE_ERROR_MAGIC_BYTE;

|

||||||

|

_currentAddress = (_startAddress + _size);

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

return true;

|

||||||

|

} else if(_command == U_SPIFFS) {

|

||||||

|

// no check of SPIFFS possible with first byte.

|

||||||

|

return true;

|

||||||

|

}

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

|

bool UpdaterClass::_verifyEnd() {

|

||||||

|

if(_command == U_FLASH) {

|

||||||

|

|

||||||

|

uint8_t buf[4];

|

||||||

|

if(!ESP.flashRead(_startAddress, (uint32_t *) &buf[0], 4)) {

|

||||||

|

_error = UPDATE_ERROR_READ;

|

||||||

|

_currentAddress = (_startAddress);

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

|

// check for valid first magic byte

|

||||||

|

if(buf[0] != 0xE9) {

|

||||||

|

_error = UPDATE_ERROR_MAGIC_BYTE;

|

||||||

|

_currentAddress = (_startAddress);

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

|

uint32_t bin_flash_size = ESP.magicFlashChipSize((buf[3] & 0xf0) >> 4);

|

||||||

|

|

||||||

|

// check if new bin fits to SPI flash

|

||||||

|

if(bin_flash_size > ESP.getFlashChipRealSize()) {

|

||||||

|

_error = UPDATE_ERROR_NEW_FLASH_CONFIG;

|

||||||

|

_currentAddress = (_startAddress);

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

|

return true;

|

||||||

|

} else if(_command == U_SPIFFS) {

|

||||||

|

// SPIFFS is already over written checks make no sense any more.

|

||||||

|

return true;

|

||||||

|

}

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

size_t UpdaterClass::writeStream(Stream &data) {

|

size_t UpdaterClass::writeStream(Stream &data) {

|

||||||

size_t written = 0;

|

size_t written = 0;

|

||||||

size_t toRead = 0;

|

size_t toRead = 0;

|

||||||

if(hasError() || !isRunning())

|

if(hasError() || !isRunning())

|

||||||

return 0;

|

return 0;

|

||||||

|

|

||||||

|

if(!_verifyHeader(data.peek())) {

|

||||||

|

#ifdef DEBUG_UPDATER

|

||||||

|

printError(DEBUG_UPDATER);

|

||||||

|

#endif

|

||||||

|

_reset();

|

||||||

|

return 0;

|

||||||

|

}

|

||||||

|

|

||||||

while(remaining()) {

|

while(remaining()) {

|

||||||

toRead = data.readBytes(_buffer + _bufferLen, (FLASH_SECTOR_SIZE - _bufferLen));

|

toRead = data.readBytes(_buffer + _bufferLen, (FLASH_SECTOR_SIZE - _bufferLen));

|

||||||

if(toRead == 0) { //Timeout

|

if(toRead == 0) { //Timeout

|

||||||

@@ -250,8 +329,9 @@ size_t UpdaterClass::writeStream(Stream &data) {

|

|||||||

#ifdef DEBUG_UPDATER

|

#ifdef DEBUG_UPDATER

|

||||||

printError(DEBUG_UPDATER);

|

printError(DEBUG_UPDATER);

|

||||||

#endif

|

#endif

|

||||||

|

_reset();

|

||||||

|

return written;

|

||||||

}

|

}

|

||||||

return written;

|

|

||||||

}

|

}

|

||||||

_bufferLen += toRead;

|

_bufferLen += toRead;

|

||||||

if((_bufferLen == remaining() || _bufferLen == FLASH_SECTOR_SIZE) && !_writeBuffer())

|

if((_bufferLen == remaining() || _bufferLen == FLASH_SECTOR_SIZE) && !_writeBuffer())

|

||||||

@@ -270,6 +350,8 @@ void UpdaterClass::printError(Stream &out){

|

|||||||

out.println("Flash Write Failed");

|

out.println("Flash Write Failed");

|

||||||

} else if(_error == UPDATE_ERROR_ERASE){

|

} else if(_error == UPDATE_ERROR_ERASE){

|

||||||

out.println("Flash Erase Failed");

|

out.println("Flash Erase Failed");

|

||||||

|

} else if(_error == UPDATE_ERROR_READ){

|

||||||

|

out.println("Flash Read Failed");

|

||||||

} else if(_error == UPDATE_ERROR_SPACE){

|

} else if(_error == UPDATE_ERROR_SPACE){

|

||||||

out.println("Not Enough Space");

|

out.println("Not Enough Space");

|

||||||

} else if(_error == UPDATE_ERROR_SIZE){

|

} else if(_error == UPDATE_ERROR_SIZE){

|

||||||

@@ -278,6 +360,12 @@ void UpdaterClass::printError(Stream &out){

|

|||||||

out.println("Stream Read Timeout");

|

out.println("Stream Read Timeout");

|

||||||

} else if(_error == UPDATE_ERROR_MD5){

|

} else if(_error == UPDATE_ERROR_MD5){

|

||||||

out.println("MD5 Check Failed");

|

out.println("MD5 Check Failed");

|

||||||

|

} else if(_error == UPDATE_ERROR_FLASH_CONFIG){

|

||||||

|

out.printf("Flash config wrong real: %d IDE: %d\n", ESP.getFlashChipRealSize(), ESP.getFlashChipSize());

|

||||||

|

} else if(_error == UPDATE_ERROR_NEW_FLASH_CONFIG){

|

||||||

|

out.printf("new Flash config wrong real: %d\n", ESP.getFlashChipRealSize());

|

||||||

|

} else if(_error == UPDATE_ERROR_MAGIC_BYTE){

|

||||||

|

out.println("Magic byte is wrong, not 0xE9");

|

||||||

} else {

|

} else {

|

||||||

out.println("UNKNOWN");

|

out.println("UNKNOWN");

|

||||||

}

|

}

|

||||||

|

|||||||

@@ -5,13 +5,18 @@

|

|||||||

#include "flash_utils.h"

|

#include "flash_utils.h"

|

||||||

#include "MD5Builder.h"

|

#include "MD5Builder.h"

|

||||||

|

|

||||||

#define UPDATE_ERROR_OK 0

|

#define UPDATE_ERROR_OK (0)

|

||||||

#define UPDATE_ERROR_WRITE 1

|

#define UPDATE_ERROR_WRITE (1)

|

||||||

#define UPDATE_ERROR_ERASE 2

|

#define UPDATE_ERROR_ERASE (2)

|

||||||

#define UPDATE_ERROR_SPACE 3

|

#define UPDATE_ERROR_READ (3)

|

||||||

#define UPDATE_ERROR_SIZE 4

|

#define UPDATE_ERROR_SPACE (4)

|

||||||

#define UPDATE_ERROR_STREAM 5

|

#define UPDATE_ERROR_SIZE (5)

|

||||||

#define UPDATE_ERROR_MD5 6

|

#define UPDATE_ERROR_STREAM (6)

|

||||||

|

#define UPDATE_ERROR_MD5 (7)

|

||||||

|

#define UPDATE_ERROR_FLASH_CONFIG (8)

|

||||||

|

#define UPDATE_ERROR_NEW_FLASH_CONFIG (9)

|

||||||

|

#define UPDATE_ERROR_MAGIC_BYTE (10)

|

||||||

|

|

||||||

|

|

||||||

#define U_FLASH 0

|

#define U_FLASH 0

|

||||||

#define U_SPIFFS 100

|

#define U_SPIFFS 100

|

||||||

@@ -63,7 +68,7 @@ class UpdaterClass {

|

|||||||

/*

|

/*

|

||||||

sets the expected MD5 for the firmware (hexString)

|

sets the expected MD5 for the firmware (hexString)

|

||||||

*/

|

*/

|

||||||

void setMD5(const char * expected_md5);

|

bool setMD5(const char * expected_md5);

|

||||||

|

|

||||||

/*

|

/*

|

||||||

returns the MD5 String of the sucessfully ended firmware

|

returns the MD5 String of the sucessfully ended firmware

|

||||||

@@ -131,6 +136,9 @@ class UpdaterClass {

|

|||||||

void _reset();

|

void _reset();

|

||||||

bool _writeBuffer();

|

bool _writeBuffer();

|

||||||

|

|

||||||

|

bool _verifyHeader(uint8_t data);

|

||||||

|

bool _verifyEnd();

|

||||||

|

|

||||||

uint8_t _error;

|

uint8_t _error;

|

||||||

uint8_t *_buffer;

|

uint8_t *_buffer;

|

||||||

size_t _bufferLen;

|

size_t _bufferLen;

|

||||||

|

|||||||

@@ -31,7 +31,7 @@ extern "C" {

|

|||||||

#include "user_interface.h"

|

#include "user_interface.h"

|

||||||

#include "cont.h"

|

#include "cont.h"

|

||||||

}

|

}

|

||||||

#define LOOP_TASK_PRIORITY 0

|

#define LOOP_TASK_PRIORITY 1

|

||||||

#define LOOP_QUEUE_SIZE 1

|

#define LOOP_QUEUE_SIZE 1

|

||||||

|

|

||||||

#define OPTIMISTIC_YIELD_TIME_US 16000

|

#define OPTIMISTIC_YIELD_TIME_US 16000

|

||||||

@@ -73,7 +73,7 @@ extern "C" void esp_yield() {

|

|||||||

}

|

}

|

||||||

|

|

||||||

extern "C" void esp_schedule() {

|

extern "C" void esp_schedule() {

|

||||||

system_os_post(LOOP_TASK_PRIORITY, 0, 0);

|

ets_post(LOOP_TASK_PRIORITY, 0, 0);

|

||||||

}

|

}

|

||||||

|

|

||||||

extern "C" void __yield() {

|

extern "C" void __yield() {

|

||||||

@@ -144,7 +144,7 @@ extern "C" void user_init(void) {

|

|||||||

|

|

||||||

cont_init(&g_cont);

|

cont_init(&g_cont);

|

||||||

|

|

||||||

system_os_task(loop_task,

|

ets_task(loop_task,

|

||||||

LOOP_TASK_PRIORITY, g_loop_queue,

|

LOOP_TASK_PRIORITY, g_loop_queue,

|

||||||

LOOP_QUEUE_SIZE);

|

LOOP_QUEUE_SIZE);

|

||||||

|

|

||||||

|

|||||||

@@ -231,6 +231,13 @@ static uint8_t phy_init_data[128] =

|

|||||||

// force_freq_offset

|

// force_freq_offset

|

||||||

// signed, unit is 8kHz

|

// signed, unit is 8kHz

|

||||||

[113] = 0,

|

[113] = 0,

|

||||||

|

|

||||||

|

// rf_cal_use_flash

|

||||||

|

// 0: RF init no RF CAL, using all RF CAL data in flash, it takes about 2ms for RF init

|

||||||

|

// 1: RF init only do TX power control CAL, others using RF CAL data in flash , it takes about 20ms for RF init

|

||||||

|

// 2: RF init no RF CAL, using all RF CAL data in flash, it takes about 2ms for RF init (same as 0?!)

|

||||||

|

// 3: RF init do all RF CAL, it takes about 200ms for RF init

|

||||||

|

[114] = 2

|

||||||

};

|

};

|

||||||

|

|

||||||

extern int __real_register_chipv6_phy(uint8_t* init_data);

|

extern int __real_register_chipv6_phy(uint8_t* init_data);

|

||||||

|

|||||||

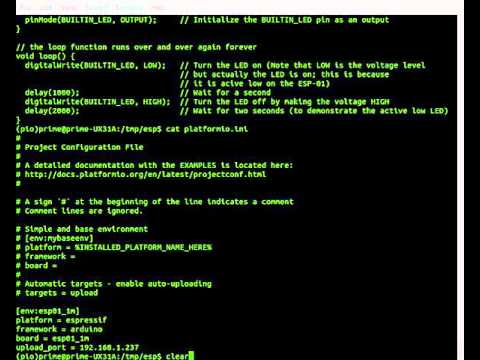

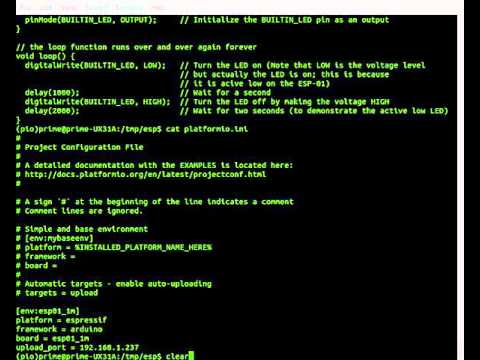

@@ -19,17 +19,24 @@ platformio boards espressif

|

|||||||

# --------------------------------------------------------------------------------------------------------

|

# --------------------------------------------------------------------------------------------------------

|

||||||

# Type MCU Frequency Flash RAM Name

|

# Type MCU Frequency Flash RAM Name

|

||||||

# --------------------------------------------------------------------------------------------------------

|

# --------------------------------------------------------------------------------------------------------

|

||||||

# esp01 esp8266 80Mhz 512Kb 32Kb Espressif ESP8266 ESP-01 board

|

# huzzah esp8266 80Mhz 1024Kb 80Kb Adafruit HUZZAH ESP8266

|

||||||

# esp01_1m esp8266 80Mhz 1024Kb 32Kb Espressif ESP8266 ESP-01-1MB board

|

# espino esp8266 80Mhz 1024Kb 80Kb ESPino

|

||||||

# esp12e esp8266 80Mhz 4096Kb 32Kb Espressif ESP8266 ESP-12E board (NodeMCU)

|

# esp12e esp8266 80Mhz 1024Kb 80Kb Espressif ESP8266 ESP-12E

|

||||||

|

# esp01 esp8266 80Mhz 512Kb 80Kb Espressif Generic ESP8266 ESP-01

|

||||||

|

# nodemcu esp8266 80Mhz 1024Kb 80Kb NodeMCU 0.9 & 1.0

|

||||||

|

# modwifi esp8266 80Mhz 1024Kb 80Kb Olimex MOD-WIFI-ESP8266(-DEV)

|

||||||

|

# thing esp8266 80Mhz 512Kb 80Kb SparkFun ESP8266 Thing

|

||||||

|

# esp210 esp8266 80Mhz 1024Kb 80Kb SweetPea ESP-210

|

||||||

|

# d1 esp8266 80Mhz 1024Kb 80Kb WeMos D1

|

||||||

|

# d1_mini esp8266 80Mhz 1024Kb 80Kb WeMos D1 mini

|

||||||

# ...

|

# ...

|

||||||

|

|

||||||

#

|

#

|

||||||

# Initialise base project

|

# Initialise base project

|

||||||

#

|

#

|

||||||

platformio init --board %TYPE%(see above)

|

platformio init --board %TYPE%(see above)

|

||||||

# for example, initialise project for ESP8266 ESP-12E board (NodeMCU)

|

# for example, initialise project for Espressif Generic ESP8266 ESP-01

|

||||||

platformio init --board esp12e

|

platformio init --board esp01

|

||||||

|

|

||||||

# The next files/directories will be created in myproject

|

# The next files/directories will be created in myproject

|

||||||

# platformio.ini - Project Configuration File. |-> PLEASE EDIT ME <-|

|

# platformio.ini - Project Configuration File. |-> PLEASE EDIT ME <-|

|

||||||

@@ -49,43 +56,14 @@ platformio run

|

|||||||

platformio run --target upload

|

platformio run --target upload

|

||||||

```

|

```

|

||||||

|

|

||||||

## OTA firmware uploading

|

## Advanced documentation

|

||||||

|

|

||||||

There are 2 options:

|

- [OTA update](http://docs.platformio.org/en/latest/platforms/espressif.html#ota-update)

|

||||||

|

* [Authentication and upload options](http://docs.platformio.org/en/latest/platforms/espressif.html#authentication-and-upload-options)

|

||||||

|

- [Custom CPU Frequency and Upload Speed](http://docs.platformio.org/en/latest/platforms/espressif.html#custom-cpu-frequency-and-upload-speed)

|

||||||

|

- [Custom Flash Size](http://docs.platformio.org/en/latest/platforms/espressif.html#custom-flash-size)

|

||||||

|

- [IDE Integration](http://docs.platformio.org/en/latest/ide.html) (Atom, CLion, Eclipse, Qt Creator, Sublime Text, VIM, Visual Studio)

|

||||||

|

- [Project Examples](http://docs.platformio.org/en/latest/platforms/espressif.html#examples)

|

||||||

|

|

||||||

- Directly specify `--upoad-port` in command line

|

## Demo of OTA update

|

||||||

```bash

|

|

||||||

platformio run --target upload --upload-port IP_ADDRESS_HERE

|

|

||||||

```

|

|

||||||

- Specify [upload_port](http://docs.platformio.org/en/latest/projectconf.html#upload-port) option in `platformio.ini`

|

|

||||||

```ini

|

|

||||||

[env:***]

|

|

||||||

...

|

|

||||||

upload_port = IP_ADDRESS_HERE

|

|

||||||

```

|

|

||||||

|

|

||||||

### Authentication and upload options

|

|

||||||

|

|

||||||

You can pass additional options/flags to OTA uploader using [upload_flags](http://docs.platformio.org/en/latest/projectconf.html#upload-flags) option in `platformio.ini`

|

|

||||||

```ini

|

|

||||||

[env:***]

|

|

||||||

upload_flags = --port=8266

|

|

||||||

```

|

|

||||||

|

|

||||||

Availalbe flags

|

|

||||||

- `--port=ESP_PORT` ESP8266 ota Port. Default 8266

|

|

||||||

- `--auth=AUTH` Set authentication password

|

|

||||||

- `--spiffs` Use this option to transmit a SPIFFS image and do not flash the module

|

|

||||||

|

|

||||||

For the full list with availalbe options please run this command `~/.platformio/packages/framework-arduinoespressif/tools/espota.py -h`.

|

|

||||||

|

|

||||||

|

|

||||||

## IDE Integration

|

|

||||||

In addition, PlatformIO [can be integrated into the popular IDEs](http://docs.platformio.org/en/latest/ide.html). For example, initialise project for Espressif ESP8266 ESP-01 board and Eclipse IDE

|

|

||||||

```

|

|

||||||

platformio init --board esp01 --ide eclipse

|

|

||||||

```

|

|

||||||

Then [import project](http://docs.platformio.org/en/latest/ide/eclipse.html) using `Eclipse Menu: File > Import... > General > Existing Projects into Workspace`.

|

|

||||||

|

|

||||||

## Demo of OTA firmware uploading

|

|

||||||

[](http://www.youtube.com/watch?v=W8wWjvQ8ZQs "PlatformIO and OTA firmware uploading to Espressif ESP8266 ESP-01")

|

[](http://www.youtube.com/watch?v=W8wWjvQ8ZQs "PlatformIO and OTA firmware uploading to Espressif ESP8266 ESP-01")

|

||||||

|

|||||||

@@ -153,7 +153,7 @@ class HTTPClient {

|

|||||||

int writeToStream(Stream * stream);

|

int writeToStream(Stream * stream);

|

||||||

String getString(void);

|

String getString(void);

|

||||||

|

|

||||||

String errorToString(int error);

|

static String errorToString(int error);

|

||||||

|

|

||||||

protected:

|

protected:

|

||||||

|

|

||||||

|

|||||||

@@ -239,6 +239,27 @@ int WiFiClient::peek()

|

|||||||

return _client->peek();

|

return _client->peek();

|

||||||

}

|

}

|

||||||

|

|

||||||

|

size_t WiFiClient::peekBytes(uint8_t *buffer, size_t length) {

|

||||||

|

size_t count = 0;

|

||||||

|

|

||||||

|

if(!_client) {

|

||||||

|

return 0;

|

||||||

|

}

|

||||||

|

|

||||||

|

_startMillis = millis();

|

||||||

|

while((available() < (int) length) && ((millis() - _startMillis) < _timeout)) {

|

||||||

|

yield();

|

||||||

|

}

|

||||||

|

|

||||||

|

if(available() < (int) length) {

|

||||||

|

count = available();

|

||||||

|

} else {

|

||||||

|

count = length;

|

||||||

|

}

|

||||||

|

|

||||||

|

return _client->peekBytes((char *)buffer, count);

|

||||||

|

}

|

||||||

|

|

||||||

void WiFiClient::flush()

|

void WiFiClient::flush()

|

||||||

{

|

{

|

||||||

if (_client)

|

if (_client)

|

||||||

|

|||||||

@@ -56,6 +56,10 @@ public:

|

|||||||

virtual int read();

|

virtual int read();

|

||||||

virtual int read(uint8_t *buf, size_t size);

|

virtual int read(uint8_t *buf, size_t size);

|

||||||

virtual int peek();

|

virtual int peek();

|

||||||

|

virtual size_t peekBytes(uint8_t *buffer, size_t length);

|

||||||

|

size_t peekBytes(char *buffer, size_t length) {

|

||||||

|

return peekBytes((uint8_t *) buffer, length);

|

||||||

|

}

|

||||||

virtual void flush();

|

virtual void flush();

|

||||||

virtual void stop();

|

virtual void stop();

|

||||||

virtual uint8_t connected();

|

virtual uint8_t connected();

|

||||||

|

|||||||

@@ -133,6 +133,17 @@ public:

|

|||||||

return _read_ptr[0];

|

return _read_ptr[0];

|

||||||

}

|

}

|

||||||

|

|

||||||

|

size_t peekBytes(char *dst, size_t size) {

|

||||||

|

if(!_available) {

|

||||||

|

if(!_readAll())

|

||||||

|

return -1;

|

||||||

|

}

|

||||||

|

|

||||||

|

size_t will_copy = (_available < size) ? _available : size;

|

||||||

|

memcpy(dst, _read_ptr, will_copy);

|

||||||

|

return will_copy;

|

||||||

|

}

|

||||||

|

|

||||||

int available() {

|

int available() {

|

||||||

auto cb = _available;

|

auto cb = _available;

|

||||||

if (cb == 0) {

|

if (cb == 0) {

|

||||||

@@ -278,6 +289,27 @@ int WiFiClientSecure::peek() {

|

|||||||

return _ssl->peek();

|

return _ssl->peek();

|

||||||

}

|

}

|

||||||

|

|

||||||

|

size_t WiFiClientSecure::peekBytes(uint8_t *buffer, size_t length) {

|

||||||

|

size_t count = 0;

|

||||||

|

|

||||||

|

if(!_ssl) {

|

||||||

|

return 0;

|

||||||

|

}

|

||||||

|

|

||||||

|

_startMillis = millis();

|

||||||

|

while((available() < (int) length) && ((millis() - _startMillis) < _timeout)) {

|

||||||

|

yield();

|

||||||

|

}

|

||||||

|

|

||||||

|

if(available() < (int) length) {

|

||||||

|

count = available();

|

||||||

|

} else {

|

||||||

|

count = length;

|

||||||

|

}

|

||||||

|

|

||||||

|

return _ssl->peekBytes((char *)buffer, count);

|

||||||

|

}

|

||||||

|

|

||||||

int WiFiClientSecure::available() {

|

int WiFiClientSecure::available() {

|

||||||

if (!_ssl)

|

if (!_ssl)

|

||||||

return 0;

|

return 0;

|

||||||

@@ -327,7 +359,7 @@ bool WiFiClientSecure::verify(const char* fp, const char* url) {

|

|||||||

int len = strlen(fp);

|

int len = strlen(fp);

|

||||||

int pos = 0;

|

int pos = 0;

|

||||||

for (size_t i = 0; i < sizeof(sha1); ++i) {

|

for (size_t i = 0; i < sizeof(sha1); ++i) {

|

||||||

while (pos < len && fp[pos] == ' ') {

|

while (pos < len && ((fp[pos] == ' ') || (fp[pos] == ':'))) {

|

||||||

++pos;

|

++pos;

|

||||||

}

|

}

|

||||||

if (pos > len - 2) {

|

if (pos > len - 2) {

|

||||||

|

|||||||

@@ -46,6 +46,7 @@ public:

|

|||||||

int available() override;

|

int available() override;

|

||||||

int read() override;

|

int read() override;

|

||||||

int peek() override;

|

int peek() override;

|

||||||

|

size_t peekBytes(uint8_t *buffer, size_t length) override;

|

||||||

void stop() override;

|

void stop() override;

|

||||||

|

|

||||||

void setCertificate(const uint8_t* cert_data, size_t size);

|

void setCertificate(const uint8_t* cert_data, size_t size);

|

||||||

|

|||||||

@@ -179,6 +179,20 @@ class ClientContext {

|

|||||||

return reinterpret_cast<char*>(_rx_buf->payload)[_rx_buf_offset];

|

return reinterpret_cast<char*>(_rx_buf->payload)[_rx_buf_offset];

|

||||||

}

|

}

|

||||||

|

|

||||||

|

size_t peekBytes(char *dst, size_t size) {

|

||||||

|

if(!_rx_buf) return 0;

|

||||||

|

|

||||||

|

size_t max_size = _rx_buf->tot_len - _rx_buf_offset;

|

||||||

|

size = (size < max_size) ? size : max_size;

|

||||||

|

|

||||||

|

DEBUGV(":pd %d, %d, %d\r\n", size, _rx_buf->tot_len, _rx_buf_offset);

|

||||||

|

size_t buf_size = _rx_buf->len - _rx_buf_offset;

|

||||||

|

size_t copy_size = (size < buf_size) ? size : buf_size;

|

||||||

|

DEBUGV(":rpi %d, %d\r\n", buf_size, copy_size);

|

||||||

|

os_memcpy(dst, reinterpret_cast<char*>(_rx_buf->payload) + _rx_buf_offset, copy_size);

|

||||||

|

return copy_size;

|

||||||

|

}

|

||||||

|

|

||||||

void flush() {

|

void flush() {

|

||||||

if(!_rx_buf) {

|

if(!_rx_buf) {

|

||||||

return;

|

return;

|

||||||

|

|||||||

@@ -51,19 +51,19 @@ typedef size_t mem_size_t;

|

|||||||

* allow these defines to be overridden.

|

* allow these defines to be overridden.

|

||||||

*/

|

*/

|

||||||

#ifndef mem_free

|

#ifndef mem_free

|

||||||

#define mem_free vPortFree

|

#define mem_free(p) vPortFree(p, "", 0)

|

||||||

#endif

|

#endif

|

||||||

#ifndef mem_malloc

|

#ifndef mem_malloc

|

||||||

#define mem_malloc pvPortMalloc

|

#define mem_malloc(s) pvPortMalloc(s, "", 0)

|

||||||

#endif

|

#endif

|

||||||

#ifndef mem_calloc

|

#ifndef mem_calloc

|

||||||

#define mem_calloc pvPortCalloc

|

#define mem_calloc(s) pvPortCalloc(s, "", 0)

|

||||||

#endif

|

#endif

|

||||||

#ifndef mem_realloc

|

#ifndef mem_realloc

|

||||||

#define mem_realloc pvPortRealloc

|

#define mem_realloc(p, s) pvPortRealloc(p, s, "", 0)

|

||||||

#endif

|

#endif

|

||||||

#ifndef mem_zalloc

|

#ifndef mem_zalloc

|

||||||

#define mem_zalloc pvPortZalloc

|

#define mem_zalloc(s) pvPortZalloc(s, "", 0)

|

||||||

#endif

|

#endif

|

||||||

|

|

||||||

#ifndef os_malloc

|

#ifndef os_malloc

|

||||||

|

|||||||

@@ -45,7 +45,7 @@ void loop() {

|

|||||||

|

|

||||||

switch(ret) {

|

switch(ret) {

|

||||||

case HTTP_UPDATE_FAILED:

|

case HTTP_UPDATE_FAILED:

|

||||||

USE_SERIAL.println("HTTP_UPDATE_FAILD");

|

USE_SERIAL.printf("HTTP_UPDATE_FAILD Error (%d): %s", ESPhttpUpdate.getLastError(), ESPhttpUpdate.getLastErrorString().c_str());

|

||||||

break;

|

break;

|

||||||

|

|

||||||

case HTTP_UPDATE_NO_UPDATES:

|

case HTTP_UPDATE_NO_UPDATES:

|

||||||

|

|||||||

@@ -48,7 +48,7 @@ void loop() {

|

|||||||

|

|

||||||

switch(ret) {

|

switch(ret) {

|

||||||

case HTTP_UPDATE_FAILED:

|

case HTTP_UPDATE_FAILED:

|

||||||

USE_SERIAL.println("HTTP_UPDATE_FAILD");

|

USE_SERIAL.printf("HTTP_UPDATE_FAILD Error (%d): %s", ESPhttpUpdate.getLastError(), ESPhttpUpdate.getLastErrorString().c_str());

|

||||||

break;

|

break;

|

||||||

|

|

||||||

case HTTP_UPDATE_NO_UPDATES:

|

case HTTP_UPDATE_NO_UPDATES:

|

||||||

|

|||||||

@@ -82,6 +82,60 @@ t_httpUpdate_return ESP8266HTTPUpdate::update(String host, uint16_t port, String

|

|||||||

return handleUpdate(&http, current_version.c_str(), reboot, false);

|

return handleUpdate(&http, current_version.c_str(), reboot, false);

|

||||||

}

|

}

|

||||||

|

|

||||||

|

/**

|

||||||

|

* return error code as int

|

||||||

|

* @return int error code

|

||||||

|

*/

|

||||||

|

int ESP8266HTTPUpdate::getLastError(void){

|

||||||

|

return lastError;

|

||||||

|

}

|

||||||

|

|

||||||

|

/**

|

||||||

|

* return error code as String

|

||||||

|

* @return String error

|

||||||

|

*/

|

||||||

|

String ESP8266HTTPUpdate::getLastErrorString(void) {

|

||||||

|

|

||||||

|

if(lastError == 0) {

|

||||||

|

return String(); // no error

|

||||||

|

}

|

||||||

|

|

||||||

|

// error from Update class

|

||||||

|

if(lastError > 0) {

|

||||||

|

StreamString error;

|

||||||

|

Update.printError(error);

|

||||||

|

error.trim(); // remove line ending

|

||||||

|

return "Update error: " + error;

|

||||||

|

}

|

||||||

|

|

||||||

|

// error from http client

|

||||||

|

if(lastError > -100) {

|

||||||

|

return "HTTP error: " + HTTPClient::errorToString(lastError);

|

||||||

|

}

|

||||||

|

|

||||||

|

switch(lastError) {

|

||||||

|

case HTTP_UE_TOO_LESS_SPACE:

|

||||||

|

return String("To less space");

|

||||||

|

case HTTP_UE_SERVER_NOT_REPORT_SIZE:

|

||||||

|

return String("Server not Report Size");

|

||||||

|

case HTTP_UE_SERVER_FILE_NOT_FOUND:

|

||||||

|

return String("File not Found (404)");

|

||||||

|

case HTTP_UE_SERVER_FORBIDDEN:

|

||||||

|

return String("Forbidden (403)");

|

||||||

|

case HTTP_UE_SERVER_WRONG_HTTP_CODE:

|

||||||

|

return String("Wrong HTTP code");

|

||||||

|

case HTTP_UE_SERVER_FAULTY_MD5:

|

||||||

|

return String("Faulty MD5");

|

||||||

|

case HTTP_UE_BIN_VERIFY_HEADER_FAILED:

|

||||||

|

return String("Verify bin header failed");

|

||||||

|

case HTTP_UE_BIN_FOR_WRONG_FLASH:

|

||||||

|

return String("bin for wrong flash size");

|

||||||

|

}

|

||||||

|

|

||||||

|

return String();

|

||||||

|

}

|

||||||

|

|

||||||

|

|

||||||

/**

|

/**

|

||||||

*

|

*

|

||||||

* @param http HTTPClient *

|

* @param http HTTPClient *

|

||||||

@@ -122,10 +176,12 @@ t_httpUpdate_return ESP8266HTTPUpdate::handleUpdate(HTTPClient * http, const cha

|

|||||||

|

|

||||||

if(code <= 0) {

|

if(code <= 0) {

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] HTTP error: %s\n", http->errorToString(code).c_str());

|

DEBUG_HTTP_UPDATE("[httpUpdate] HTTP error: %s\n", http->errorToString(code).c_str());

|

||||||

|

lastError = code;

|

||||||

http->end();

|

http->end();

|

||||||

return HTTP_UPDATE_FAILED;

|

return HTTP_UPDATE_FAILED;

|

||||||

}

|

}

|

||||||

|

|

||||||

|

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] Header read fin.\n");

|

DEBUG_HTTP_UPDATE("[httpUpdate] Header read fin.\n");

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] Server header:\n");

|

DEBUG_HTTP_UPDATE("[httpUpdate] Server header:\n");

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] - code: %d\n", code);

|

DEBUG_HTTP_UPDATE("[httpUpdate] - code: %d\n", code);

|

||||||

@@ -161,6 +217,7 @@ t_httpUpdate_return ESP8266HTTPUpdate::handleUpdate(HTTPClient * http, const cha

|

|||||||

}

|

}

|

||||||

|

|

||||||

if(!startUpdate) {

|

if(!startUpdate) {

|

||||||

|

lastError = HTTP_UE_TOO_LESS_SPACE;

|

||||||

ret = HTTP_UPDATE_FAILED;

|

ret = HTTP_UPDATE_FAILED;

|

||||||

} else {

|

} else {

|

||||||

|

|

||||||

@@ -181,6 +238,33 @@ t_httpUpdate_return ESP8266HTTPUpdate::handleUpdate(HTTPClient * http, const cha

|

|||||||

DEBUG_HTTP_UPDATE("[httpUpdate] runUpdate flash...\n");

|

DEBUG_HTTP_UPDATE("[httpUpdate] runUpdate flash...\n");

|

||||||

}

|

}

|

||||||

|

|

||||||

|

uint8_t buf[4];

|

||||||

|

if(tcp->peekBytes(&buf[0], 4) != 4) {

|

||||||

|

DEBUG_HTTP_UPDATE("[httpUpdate] peekBytes magic header failed\n");

|

||||||

|

lastError = HTTP_UE_BIN_VERIFY_HEADER_FAILED;

|

||||||

|

http->end();

|

||||||

|

return HTTP_UPDATE_FAILED;

|

||||||

|

}

|

||||||

|

|

||||||

|

// check for valid first magic byte

|

||||||

|

if(buf[0] != 0xE9) {

|

||||||

|

DEBUG_HTTP_UPDATE("[httpUpdate] magic header not starts with 0xE9\n");

|

||||||

|

lastError = HTTP_UE_BIN_VERIFY_HEADER_FAILED;

|

||||||

|

http->end();

|

||||||

|

return HTTP_UPDATE_FAILED;

|

||||||

|

|

||||||

|

}

|

||||||

|

|

||||||

|

uint32_t bin_flash_size = ESP.magicFlashChipSize((buf[3] & 0xf0) >> 4);

|

||||||

|

|

||||||

|

// check if new bin fits to SPI flash

|

||||||

|

if(bin_flash_size > ESP.getFlashChipRealSize()) {

|

||||||

|

DEBUG_HTTP_UPDATE("[httpUpdate] magic header, new bin not fits SPI Flash\n");

|

||||||

|

lastError = HTTP_UE_BIN_FOR_WRONG_FLASH;

|

||||||

|

http->end();

|

||||||

|

return HTTP_UPDATE_FAILED;

|

||||||

|

}

|

||||||

|

|

||||||

if(runUpdate(*tcp, len, http->header("x-MD5"), command)) {

|

if(runUpdate(*tcp, len, http->header("x-MD5"), command)) {

|

||||||

ret = HTTP_UPDATE_OK;

|

ret = HTTP_UPDATE_OK;

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] Update ok\n");

|

DEBUG_HTTP_UPDATE("[httpUpdate] Update ok\n");

|

||||||

@@ -196,6 +280,7 @@ t_httpUpdate_return ESP8266HTTPUpdate::handleUpdate(HTTPClient * http, const cha

|

|||||||

}

|

}

|

||||||

}

|

}

|

||||||

} else {

|

} else {

|

||||||

|

lastError = HTTP_UE_SERVER_NOT_REPORT_SIZE;

|

||||||

ret = HTTP_UPDATE_FAILED;

|

ret = HTTP_UPDATE_FAILED;

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] Content-Length is 0 or not set by Server?!\n");

|

DEBUG_HTTP_UPDATE("[httpUpdate] Content-Length is 0 or not set by Server?!\n");

|

||||||

}

|

}

|

||||||

@@ -204,16 +289,23 @@ t_httpUpdate_return ESP8266HTTPUpdate::handleUpdate(HTTPClient * http, const cha

|

|||||||

///< Not Modified (No updates)

|

///< Not Modified (No updates)

|

||||||

ret = HTTP_UPDATE_NO_UPDATES;

|

ret = HTTP_UPDATE_NO_UPDATES;

|

||||||

break;

|

break;

|

||||||

|

case HTTP_CODE_NOT_FOUND:

|

||||||

|

lastError = HTTP_UE_SERVER_FILE_NOT_FOUND;

|

||||||

|

ret = HTTP_UPDATE_FAILED;

|

||||||

|

break;

|

||||||

|

case HTTP_CODE_FORBIDDEN:

|

||||||

|

lastError = HTTP_UE_SERVER_FORBIDDEN;

|

||||||

|

ret = HTTP_UPDATE_FAILED;

|

||||||

|

break;

|

||||||

default:

|

default:

|

||||||

|

lastError = HTTP_UE_SERVER_WRONG_HTTP_CODE;

|

||||||

ret = HTTP_UPDATE_FAILED;

|

ret = HTTP_UPDATE_FAILED;

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] HTTP Code is (%d)\n", code);

|

DEBUG_HTTP_UPDATE("[httpUpdate] HTTP Code is (%d)\n", code);

|

||||||

//http->writeToStream(&Serial1);

|

//http->writeToStream(&Serial1);

|

||||||

break;

|

break;

|

||||||

}

|

}

|

||||||

|

|

||||||

|

|

||||||

http->end();

|

http->end();

|

||||||

|

|

||||||

return ret;

|

return ret;

|

||||||

}

|

}

|

||||||

|

|

||||||

@@ -229,6 +321,7 @@ bool ESP8266HTTPUpdate::runUpdate(Stream& in, uint32_t size, String md5, int com

|

|||||||

StreamString error;

|

StreamString error;

|

||||||

|

|

||||||

if(!Update.begin(size, command)) {

|

if(!Update.begin(size, command)) {

|

||||||

|

lastError = Update.getError();

|

||||||

Update.printError(error);

|

Update.printError(error);

|

||||||

error.trim(); // remove line ending

|

error.trim(); // remove line ending

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] Update.begin failed! (%s)\n", error.c_str());

|

DEBUG_HTTP_UPDATE("[httpUpdate] Update.begin failed! (%s)\n", error.c_str());

|

||||||

@@ -236,10 +329,15 @@ bool ESP8266HTTPUpdate::runUpdate(Stream& in, uint32_t size, String md5, int com

|

|||||||

}

|

}

|

||||||

|

|

||||||

if(md5.length()) {

|

if(md5.length()) {

|

||||||

Update.setMD5(md5.c_str());

|

if(!Update.setMD5(md5.c_str())) {

|

||||||

|

lastError = HTTP_UE_SERVER_FAULTY_MD5;

|

||||||

|

DEBUG_HTTP_UPDATE("[httpUpdate] Update.setMD5 failed! (%s)\n", md5.c_str());

|

||||||

|

return false;

|

||||||

|

}

|

||||||

}

|

}

|

||||||

|

|

||||||

if(Update.writeStream(in) != size) {

|

if(Update.writeStream(in) != size) {

|

||||||

|

lastError = Update.getError();

|

||||||

Update.printError(error);

|

Update.printError(error);

|

||||||

error.trim(); // remove line ending

|

error.trim(); // remove line ending

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] Update.writeStream failed! (%s)\n", error.c_str());

|

DEBUG_HTTP_UPDATE("[httpUpdate] Update.writeStream failed! (%s)\n", error.c_str());

|

||||||

@@ -247,6 +345,7 @@ bool ESP8266HTTPUpdate::runUpdate(Stream& in, uint32_t size, String md5, int com

|

|||||||

}

|

}

|

||||||

|

|

||||||

if(!Update.end()) {

|

if(!Update.end()) {

|

||||||

|

lastError = Update.getError();

|

||||||

Update.printError(error);

|

Update.printError(error);

|

||||||

error.trim(); // remove line ending

|

error.trim(); // remove line ending

|

||||||

DEBUG_HTTP_UPDATE("[httpUpdate] Update.end failed! (%s)\n", error.c_str());

|

DEBUG_HTTP_UPDATE("[httpUpdate] Update.end failed! (%s)\n", error.c_str());

|

||||||

|

|||||||

@@ -38,6 +38,16 @@

|

|||||||

#define DEBUG_HTTP_UPDATE(...)

|

#define DEBUG_HTTP_UPDATE(...)

|

||||||

#endif

|

#endif

|

||||||

|

|

||||||

|

/// note we use HTTP client errors too so we start at 100

|

||||||

|

#define HTTP_UE_TOO_LESS_SPACE (-100)

|

||||||

|

#define HTTP_UE_SERVER_NOT_REPORT_SIZE (-101)

|

||||||

|

#define HTTP_UE_SERVER_FILE_NOT_FOUND (-102)

|

||||||

|

#define HTTP_UE_SERVER_FORBIDDEN (-103)

|

||||||

|

#define HTTP_UE_SERVER_WRONG_HTTP_CODE (-104)

|

||||||

|

#define HTTP_UE_SERVER_FAULTY_MD5 (-105)

|

||||||

|

#define HTTP_UE_BIN_VERIFY_HEADER_FAILED (-106)

|

||||||

|

#define HTTP_UE_BIN_FOR_WRONG_FLASH (-107)

|

||||||

|

|

||||||

typedef enum {

|

typedef enum {

|

||||||

HTTP_UPDATE_FAILED,

|

HTTP_UPDATE_FAILED,

|

||||||

HTTP_UPDATE_NO_UPDATES,

|

HTTP_UPDATE_NO_UPDATES,

|

||||||

@@ -55,9 +65,14 @@ class ESP8266HTTPUpdate {

|

|||||||

|

|

||||||

t_httpUpdate_return updateSpiffs(const char * url, const char * current_version = "", const char * httpsFingerprint = "", bool reboot = false);

|

t_httpUpdate_return updateSpiffs(const char * url, const char * current_version = "", const char * httpsFingerprint = "", bool reboot = false);

|

||||||

|

|

||||||

|

int getLastError(void);

|

||||||

|

String getLastErrorString(void);

|

||||||

|

|

||||||

protected:

|

protected:

|

||||||

t_httpUpdate_return handleUpdate(HTTPClient * http, const char * current_version, bool reboot = true, bool spiffs = false);

|

t_httpUpdate_return handleUpdate(HTTPClient * http, const char * current_version, bool reboot = true, bool spiffs = false);

|

||||||

bool runUpdate(Stream& in, uint32_t size, String md5, int command = U_FLASH);

|

bool runUpdate(Stream& in, uint32_t size, String md5, int command = U_FLASH);

|

||||||

|

|

||||||

|

int lastError;

|

||||||

};

|

};

|

||||||

|

|

||||||

extern ESP8266HTTPUpdate ESPhttpUpdate;

|

extern ESP8266HTTPUpdate ESPhttpUpdate;

|

||||||

|

|||||||

@@ -85,21 +85,42 @@ static const IPAddress MDNS_MULTICAST_ADDR(224, 0, 0, 251);

|

|||||||

static const int MDNS_MULTICAST_TTL = 1;

|

static const int MDNS_MULTICAST_TTL = 1;

|

||||||

static const int MDNS_PORT = 5353;

|

static const int MDNS_PORT = 5353;

|

||||||

|

|

||||||

MDNSResponder::MDNSResponder() : _conn(0) { _services = 0; _arduinoAuth = false; }

|

struct MDNSService {

|

||||||

|

MDNSService* _next;

|

||||||

|

char _name[32];

|

||||||

|

char _proto[3];

|

||||||

|

uint16_t _port;

|

||||||

|

struct MDNSTxt * _txts;

|

||||||

|

uint16_t _txtLen; // length of all txts

|

||||||

|

};

|

||||||

|

|

||||||

|

struct MDNSTxt{

|

||||||

|

MDNSTxt * _next;

|

||||||

|

String _txt;

|

||||||

|

};

|

||||||

|

|

||||||

|

|

||||||

|

|

||||||

|

MDNSResponder::MDNSResponder() : _conn(0) {

|

||||||

|

_services = 0;

|

||||||

|

_instanceName = "";

|

||||||

|

}

|

||||||

MDNSResponder::~MDNSResponder() {}

|

MDNSResponder::~MDNSResponder() {}

|

||||||

|

|

||||||

bool MDNSResponder::begin(const char* domain){

|

bool MDNSResponder::begin(const char* hostname){

|

||||||

// Open the MDNS socket if it isn't already open.

|

// Open the MDNS socket if it isn't already open.

|

||||||

|

|

||||||

size_t n = strlen(domain);

|

size_t n = strlen(hostname);

|

||||||

if (n > 255) { // Can only handle domains that are 255 chars in length.

|

if (n > 63) { // max size for a single label.

|

||||||

return false;

|

return false;

|

||||||

}

|

}

|

||||||

|

|

||||||

// Copy in domain characters as lowercase

|

// Copy in hostname characters as lowercase

|

||||||

for (size_t i = 0; i < n; ++i)

|

_hostName = hostname;

|

||||||

_hostName[i] = tolower(domain[i]);

|

_hostName.toLowerCase();

|

||||||

_hostName[n] = '\0';

|

|

||||||

|

// If instance name is not already set copy hostname to instance name

|

||||||

|

if (_instanceName.equals("") ) _instanceName=hostname;

|

||||||

|

|

||||||

// Open the MDNS socket if it isn't already open.

|

// Open the MDNS socket if it isn't already open.

|

||||||

if (!_conn) {

|

if (!_conn) {

|

||||||

@@ -138,6 +159,48 @@ void MDNSResponder::update() {

|

|||||||

_parsePacket();

|

_parsePacket();

|

||||||

}

|

}

|

||||||

|

|

||||||

|

|

||||||

|

void MDNSResponder::setInstanceName(String name){

|

||||||

|

if (name.length() > 63) return;

|

||||||

|

else _instanceName = name;

|

||||||

|

}

|

||||||

|

|

||||||

|

|

||||||

|

bool MDNSResponder::addServiceTxt(char *name, char *proto, char *key, char *value){

|

||||||

|

MDNSService* servicePtr;

|

||||||

|

|

||||||

|

uint8_t txtLen = os_strlen(key) + os_strlen(value) + 1; // Add one for equals sign

|

||||||

|

txtLen+=1; //accounts for length byte added when building the txt responce

|

||||||

|

//Find the service

|

||||||

|

for (servicePtr = _services; servicePtr; servicePtr = servicePtr->_next) {

|

||||||

|

//Checking Service names

|

||||||

|

if(strcmp(servicePtr->_name, name) == 0 && strcmp(servicePtr->_proto, proto) == 0){

|

||||||

|

//found a service name match

|

||||||

|

if (servicePtr->_txtLen + txtLen > 1300) return false; //max txt record size

|

||||||

|

MDNSTxt *newtxt = new MDNSTxt;

|

||||||

|

newtxt->_txt = String(key) + "=" + String(value);

|

||||||

|

newtxt->_next = 0;

|

||||||

|

if(servicePtr->_txts == 0) { //no services have been added

|

||||||

|

//Adding First TXT to service

|

||||||

|

servicePtr->_txts = newtxt;

|

||||||

|

servicePtr->_txtLen += txtLen;

|

||||||

|

return true;

|

||||||

|

}

|

||||||

|

else{

|

||||||

|

MDNSTxt * txtPtr = servicePtr->_txts;

|

||||||

|

while(txtPtr->_next !=0) {

|

||||||

|

txtPtr = txtPtr->_next;

|

||||||

|

}

|

||||||

|

//adding another TXT to service

|

||||||

|

txtPtr->_next = newtxt;

|

||||||

|

servicePtr->_txtLen += txtLen;

|

||||||

|

return true;

|

||||||

|

}

|

||||||

|

}

|

||||||

|

}

|

||||||

|

return false;

|

||||||

|

}

|

||||||

|

|

||||||

void MDNSResponder::addService(char *name, char *proto, uint16_t port){

|

void MDNSResponder::addService(char *name, char *proto, uint16_t port){

|

||||||

if(_getServicePort(name, proto) != 0) return;

|

if(_getServicePort(name, proto) != 0) return;

|

||||||

if(os_strlen(name) > 32 || os_strlen(proto) != 3) return; //bad arguments

|

if(os_strlen(name) > 32 || os_strlen(proto) != 3) return; //bad arguments

|

||||||

@@ -146,8 +209,42 @@ void MDNSResponder::addService(char *name, char *proto, uint16_t port){

|

|||||||

os_strcpy(srv->_proto, proto);

|

os_strcpy(srv->_proto, proto);

|

||||||

srv->_port = port;

|

srv->_port = port;

|

||||||

srv->_next = 0;

|

srv->_next = 0;

|

||||||

if(_services) _services->_next = srv;

|

srv->_txts = 0;

|

||||||

else _services = srv;

|

srv->_txtLen = 0;

|

||||||

|

|

||||||

|

if(_services == 0) _services = srv;

|

||||||

|

else{

|

||||||

|

MDNSService* servicePtr = _services;

|

||||||

|

while(servicePtr->_next !=0) servicePtr = servicePtr->_next;

|

||||||

|

servicePtr->_next = srv;

|

||||||

|

}

|

||||||

|

|

||||||

|

}

|

||||||

|

|

||||||

|

MDNSTxt * MDNSResponder::_getServiceTxt(char *name, char *proto){

|

||||||

|

MDNSService* servicePtr;

|

||||||

|

for (servicePtr = _services; servicePtr; servicePtr = servicePtr->_next) {

|

||||||

|

if(servicePtr->_port > 0 && strcmp(servicePtr->_name, name) == 0 && strcmp(servicePtr->_proto, proto) == 0){

|

||||||

|

if (servicePtr->_txts == 0) return false;

|

||||||

|

else{

|

||||||

|

return servicePtr->_txts;

|

||||||

|

}

|

||||||

|

}

|

||||||

|

}

|

||||||

|

return 0;

|

||||||

|

}

|

||||||

|

|

||||||

|

uint16_t MDNSResponder::_getServiceTxtLen(char *name, char *proto){

|

||||||

|

MDNSService* servicePtr;

|

||||||

|

for (servicePtr = _services; servicePtr; servicePtr = servicePtr->_next) {

|

||||||

|

if(servicePtr->_port > 0 && strcmp(servicePtr->_name, name) == 0 && strcmp(servicePtr->_proto, proto) == 0){

|

||||||

|

if (servicePtr->_txts == 0) return false;

|

||||||

|

else{

|

||||||

|

return servicePtr->_txtLen;

|

||||||

|

}

|

||||||

|

}

|

||||||

|

}

|

||||||

|

return 0;

|

||||||

}

|

}

|

||||||

|

|

||||||

uint16_t MDNSResponder::_getServicePort(char *name, char *proto){

|

uint16_t MDNSResponder::_getServicePort(char *name, char *proto){

|

||||||

@@ -172,7 +269,7 @@ uint32_t MDNSResponder::_getOurIp(){

|

|||||||

return staIpInfo.ip.addr;

|

return staIpInfo.ip.addr;

|

||||||

} else {

|

} else {

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_NO_LOCAL_IP\n");

|

Serial.printf("ERR_NO_LOCAL_IP\n");

|

||||||

#endif

|

#endif

|

||||||

return 0;

|

return 0;

|

||||||

}

|

}

|

||||||

@@ -217,9 +314,11 @@ void MDNSResponder::_parsePacket(){

|

|||||||

hostNameLen = 0;

|

hostNameLen = 0;

|

||||||

}

|

}

|

||||||

|

|

||||||

if(hostNameLen > 0 && strcmp(_hostName, hostName) != 0){

|

if(hostNameLen > 0 && !_hostName.equals(hostName) && !_instanceName.equals(hostName)){

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_NO_HOST: %s\n", hostName);

|

Serial.printf("ERR_NO_HOST: %s\n", hostName);

|

||||||

|

Serial.printf("hostname: %s\n", _hostName.c_str() );

|

||||||

|

Serial.printf("instance: %s\n", _instanceName.c_str() );

|

||||||

#endif

|

#endif

|

||||||

_conn->flush();

|

_conn->flush();

|

||||||

return;

|

return;

|

||||||

@@ -244,14 +343,14 @@ void MDNSResponder::_parsePacket(){

|

|||||||

localParsed = true;

|

localParsed = true;

|

||||||

} else {

|

} else {

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_FQDN: %s\n", serviceName);

|

Serial.printf("ERR_FQDN: %s\n", serviceName);

|

||||||

#endif

|

#endif

|

||||||

_conn->flush();

|

_conn->flush();

|

||||||

return;

|

return;

|

||||||

}

|

}

|

||||||

} else {

|

} else {

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_SERVICE: %s\n", serviceName);

|

Serial.printf("ERR_SERVICE: %s\n", serviceName);

|

||||||

#endif

|

#endif

|

||||||

_conn->flush();

|

_conn->flush();

|

||||||

return;

|

return;

|

||||||

@@ -268,7 +367,7 @@ void MDNSResponder::_parsePacket(){

|

|||||||

protoParsed = true;

|

protoParsed = true;

|

||||||

} else {

|

} else {

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_PROTO: %s\n", protoName);

|

Serial.printf("ERR_PROTO: %s\n", protoName);

|

||||||

#endif

|

#endif

|

||||||

_conn->flush();

|

_conn->flush();

|

||||||

return;

|

return;

|

||||||

@@ -285,7 +384,7 @@ void MDNSResponder::_parsePacket(){

|

|||||||

localParsed = true;

|

localParsed = true;

|

||||||

} else {

|

} else {

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_FQDN: %s\n", localName);

|

Serial.printf("ERR_FQDN: %s\n", localName);

|

||||||

#endif

|

#endif

|

||||||

_conn->flush();

|

_conn->flush();

|

||||||

return;

|

return;

|

||||||

@@ -296,14 +395,14 @@ void MDNSResponder::_parsePacket(){

|

|||||||

servicePort = _getServicePort(serviceName, protoName);

|

servicePort = _getServicePort(serviceName, protoName);

|

||||||

if(servicePort == 0){

|

if(servicePort == 0){

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_NO_SERVICE: %s\n", serviceName);

|

Serial.printf("ERR_NO_SERVICE: %s\n", serviceName);

|

||||||

#endif

|

#endif

|

||||||

_conn->flush();

|

_conn->flush();

|

||||||

return;

|

return;

|

||||||

}

|

}

|

||||||

} else if(serviceNameLen > 0 || protoNameLen > 0){

|

} else if(serviceNameLen > 0 || protoNameLen > 0){

|

||||||

#ifdef MDNS_DEBUG_ERR

|

#ifdef MDNS_DEBUG_ERR

|

||||||

os_printf("ERR_SERVICE_PROTO: %s\n", serviceName);

|

Serial.printf("ERR_SERVICE_PROTO: %s\n", serviceName);

|

||||||

#endif

|

#endif

|

||||||

_conn->flush();

|

_conn->flush();

|

||||||

return;

|

return;

|

||||||

@@ -312,7 +411,7 @@ void MDNSResponder::_parsePacket(){

|

|||||||

// RESPOND

|

// RESPOND

|

||||||

|

|

||||||

#ifdef MDNS_DEBUG_RX

|

#ifdef MDNS_DEBUG_RX

|

||||||

os_printf("RX: REQ, ID:%u, Q:%u, A:%u, NS:%u, ADD:%u\n", packetHeader[0], packetHeader[2], packetHeader[3], packetHeader[4], packetHeader[5]);

|

Serial.printf("RX: REQ, ID:%u, Q:%u, A:%u, NS:%u, ADD:%u\n", packetHeader[0], packetHeader[2], packetHeader[3], packetHeader[4], packetHeader[5]);

|

||||||

#endif

|

#endif

|

||||||

|

|

||||||

uint16_t currentType;

|

uint16_t currentType;

|

||||||

@@ -339,24 +438,24 @@ void MDNSResponder::_parsePacket(){

|

|||||||

}

|

}

|

||||||

|

|

||||||

#ifdef MDNS_DEBUG_RX

|

#ifdef MDNS_DEBUG_RX

|

||||||

os_printf("REQ: ");

|

Serial.printf("REQ: ");

|

||||||

if(hostNameLen > 0) os_printf("%s.", hostName);

|

if(hostNameLen > 0) Serial.printf("%s.", hostName);

|